## 【19】中華民國

## 【12】專利公報 (B)

【11】證書號數: I508449

【45】公告日: 中華民國 104 (2015) 年 11 月 11 日 【51】Int. Cl.: *H03K23/54 (2006.01)*

發明 全4頁

【54】名 稱:分數式線性回授移位暫存器

FRACTIONAL LINEAR FEEDBACK SHIFT REGISTER

【21】申請案號:102129110 【11】公開編號:201507357 【43】公開日期:中華民國 102 (2013) 年 08 月 14 日 【43】公開日期:中華民國 104 (2015) 年 02 月 16 日

【72】發明人: 陳寶龍 (TW) CHEN, PAO LUNG

【71】申 請 人: 國立高雄第一科技大學 NATIONAL KAOHSIUNG FIRST

UNIVERSITY OF SCIENCE AND

**TECHNOLOGY**

高雄市楠梓區卓越路 2 號

【74】代理人: 陳豐裕

【56】參考文獻:

TW 200732961A US 20060174066A1

US 20120139592A1

2010年9月30日公開文件 Victor Rodolfo Gonzalez-Diaz "Efficient

Dithering in MASH Sigma-Delta Modulators for Fractional Frequency Synthesizers" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS

審查人員:蘇齊賢

## [57]申請專利範圍

- 1. 一種分數式線性回授移位暫存器,其主要係包括有由時脈〔clock〕控制之輸入暫存器、分數式線性回授移位暫存器產生器及計數輸出單元;其中:該輸入暫存器,其供輸入信號連結輸入,且令該輸入暫存器連接至該計數輸出單元,該輸入暫存器供儲存輸入分數值;該分數式線性回授移位暫存器產生器〔Fractional Linear Feedback Shift Register〕,其與該計數輸出單元相連接,該分數式線性回授移位暫存器產生器包含有一個線性回授移位暫存器控制單元、與該線性回授移位暫存器控制單元連接之 m 個 D 型正反器、及受該線性回授移位暫存器控制單元連接控制之 2x1 多工器,而該線性回授移位暫存器控制單元包含有偵測裝置、與該偵測裝置連接為該 D 型正反器之除頻器、及分別與該偵測裝置和該除頻器連接之線性回授移位暫存器不同函數選擇單元,該偵測裝置係供偵測該分數式線性回授移位暫存器產生器之各該 D 型正反器的輸出端全為 0,該線性回授移位暫存器不同函數選擇單元可供將函數控制號信號進行儲存;該計數輸出單元,其包含有N-1 位元之計數器、與該計數器連接之比較器、與該計數器及該比較器連接之該 2x1 多工器、與該 2x1 多工器連接之該 D 型正反器。

- 2. 如申請專利範圍第 1 項所述分數式線性回授移位暫存器,其中,該線性回授移位暫存器不同函數選擇單元包含有線性回授移位暫存器控制字元組、與該線性回授移位暫存器控制字元組連接之該 2x1 多工器、與該 2x1 多工器連接之控制字元暫存器及該計數器。

## 圖式簡單說明

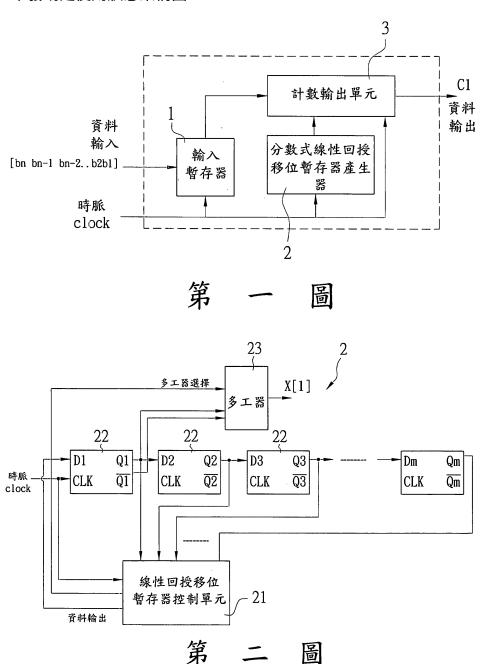

第一圖:本發明之架構圖

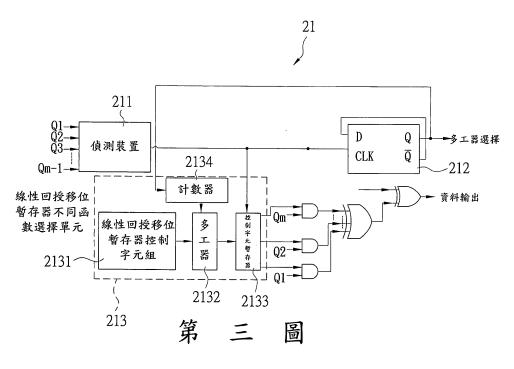

第二圖:本發明之分數式線性回授移位暫存器產生器架構圖

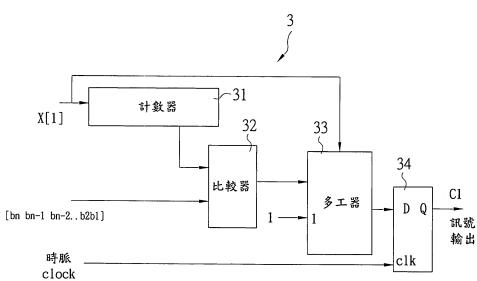

第三圖:本發明之線性回授移位暫存器控制單元架構圖

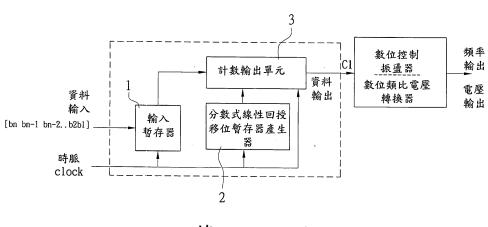

第四圖:本發明之計數輸出單元架構圖

第五圖:本發明之使用狀態架構圖

- 11972 -

第四圖

第 五 圖